A flexible instruction template system

The ForwardCom instruction set is based on a consistent and flexible

modular format suitable for fast superscalar processors. Each

instruction uses one, two, or three 32-bit words.

It is possible to add still longer

instructions for application-specific purposes.

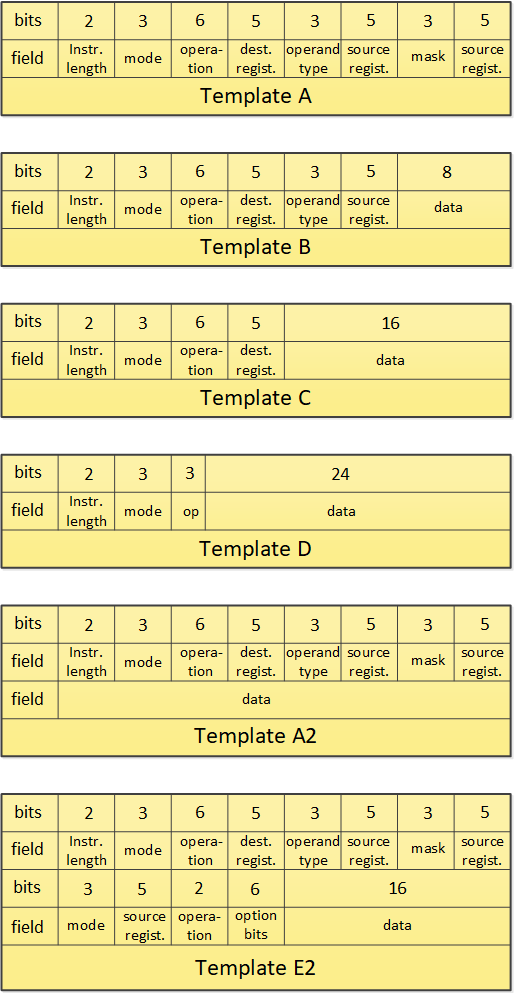

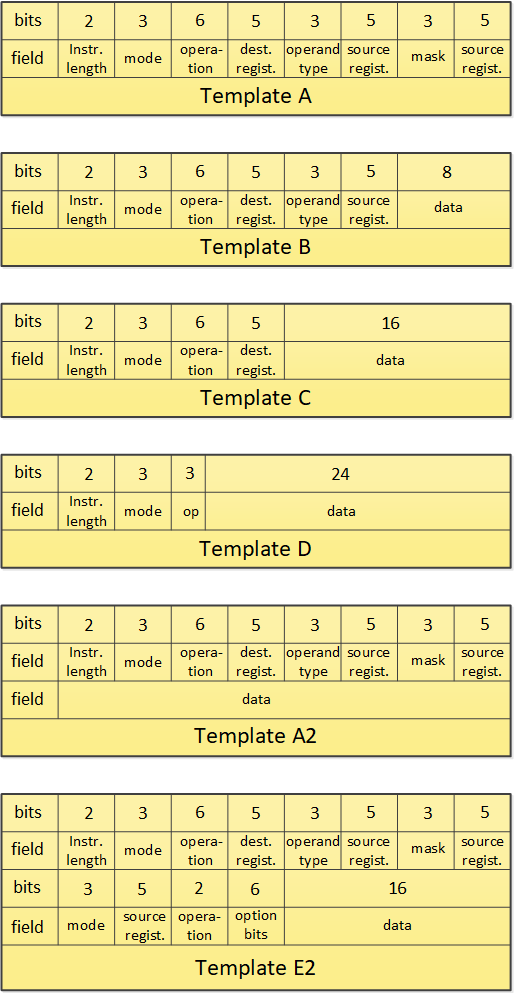

A sketch of the instruction format template system is shown here:

The basic instruction word is 32 bits, divided into the following

fields:

- Instruction length

- Tells whether the instruction uses one, two, or three 32-bit words.

- Mode

- Tells which template is used, what the different fields are used

for, whether the instruction uses general purpose registers or

vector registers, whether there is a memory operand, and which

addressing mode is used.

- Operation

- Tells what instruction to do. There can be up to 64 multi-format

instructions. A multi-format instruction can have many different

formats, instruction lengths, and addressing modes. In addition,

there can be a large number of single-format instructions. One

operation code in ForwardCom corresponds to multiple different

operation codes in other systems because it can have several

different operand types, register types, vector lengths, masks,

addressing modes, etc.

- Destination register

- There are 32 general purpose registers and 32 vector registers.

The register specified in this field is used for the destination

(output) of the instruction. The same register is also used as

source (input) if there are not enough source registers in the other

fields.

- Operand type

- The operands can be 8-bit, 16-bit, 32-bit, and 64-bit integers and

half, single, and double precision floating point numbers.

There is optional support for 128-bit integers and quadruple precision floating point numbers.

- Source register

- There can be one, two, or three source registers depending on which template is used.

The source registers can be general purpose registers or vector registers.

They can also be used for memory pointers, array index, or for specifying vector length.

- Mask

- A general purpose register or vector register can be used as a mask or predicate to enable or disable the operation and to specify various options.

Masks are particularly useful for vector operations where an operation can be enabled or

disabled for each vector element separately.

- Data

- Data fields can be used for immediate operands and for relative

addresses.

The data fields are aligned and contiguous with mostly power-of-2 sizes.

Instructions with double length can have 32-bit data fields.

The A2 and E2 templates can be extended to triple length by adding an extra 32-bit

data field to make room for up to 64 bits of data.

Data fields can contain integer or floating point numbers.

Data with few significant bits are automatically compressed into

the smallest field size that fits the actual value.

- Option bits

- These bits are used for instruction-specific options and for making

different variants of an instruction.